flowchart TD

A["ISA - Interface Hardware/Software<br/>(O que é o conjunto de instruções)"]

B["Anatomia de uma Instrução<br/>(Opcode, Operandos, Formato)"]

C["Modos de Endereçamento<br/>(Imediato, Direto, Indireto,<br/>Registrador, Indexado)"]

D["Filosofia CISC vs RISC<br/>(Trade-offs de projeto)"]

E["ISA do PIC18F4550<br/>(75 instruções organizadas<br/>por categoria)"]

F["Análise de Assembly Gerado<br/>(C → Assembly)"]

G["Projeto Integrador<br/>(Análise de Assembly,<br/>Implementação em Assembly,<br/>Documentação de Modos)"]

H["Módulo 2<br/>(Representação de Dados)"]

I["Módulo 4<br/>(Caminho de Dados da CPU)"]

H --> A

A --> B

B --> C

B --> D

D --> E

C --> E

E --> F

F --> G

C --> G

I -.->|"próximo módulo"| E

Módulo 3: Conjunto de Instruções e Modos de Endereçamento

Seja bem-vindo ao terceiro módulo da disciplina de Arquitetura e Organização de Computadores. Neste material você vai cruzar a fronteira entre o hardware e o software pela primeira vez — e essa fronteira tem um nome preciso: o conjunto de instruções. Prepare-se para entender o que o processador realmente faz quando executa seu código, e por que certas escolhas de projeto determinam o desempenho de sistemas inteiros. Estude com atenção, porque o que você vai aprender aqui conecta tudo que veio antes com tudo que vem depois.

Por Que Isso Importa Para Você?

Imagine que você escreveu uma função em C para calcular a média de um vetor de temperaturas lidas pelo sensor do seu kit ACEPIC PRO V8.2. O código funciona perfeitamente, mas você percebe que ele está demorando mais do que o esperado — o display LCD trava por uma fração de segundo a cada atualização. Você tenta otimizar, mas não sabe por onde começar. O que está acontecendo por baixo dos panos?

A resposta está no conjunto de instruções do processador. Quando você escreve media = soma / n; em C, o compilador traduz essa divisão para uma sequência de instruções de máquina que o PIC18F4550 pode executar. Se você não sabe quais instruções estão sendo geradas, como elas acessam os dados na memória e quantos ciclos de clock cada uma consome, você está voando às cegas na hora de otimizar.

Mas esse conhecimento vai além da otimização. Compreender o conjunto de instruções — o que os projetistas de hardware chamam de Instruction Set Architecture (ISA) — é fundamental para entender por que existem arquiteturas diferentes no mundo. Por que o processador do seu computador é completamente diferente do PIC? Por que um smartphone usa um chip diferente de um servidor? Essas questões têm respostas profundas que começam exatamente aqui.

Neste módulo, você vai aprender a anatomia de uma instrução de máquina, os diferentes modos pelos quais uma instrução pode encontrar seus dados (os chamados modos de endereçamento), a filosofia por trás das arquiteturas RISC e CISC, e os detalhes do conjunto de instruções do PIC18F4550. Ao final, você estará pronto para analisar o código assembly gerado pelo compilador e até mesmo escrever funções críticas diretamente em assembly — exatamente o que o Projeto Integrador vai pedir.

O diagrama abaixo mostra como os temas deste módulo se relacionam entre si e com os conceitos que você já estudou:

A Interface Entre Hardware e Software: O Que É uma ISA?

Toda vez que você escreve um programa em C, Python ou qualquer outra linguagem, você está se comunicando com o computador em um nível de abstração alto — próximo do raciocínio humano. Mas o processador não entende C. Ele entende apenas uma linguagem muito mais primitiva: sequências de bits que codificam operações específicas. Essa linguagem tem um nome técnico: Instruction Set Architecture, ou simplesmente ISA.

A ISA é a especificação completa de tudo que um processador pode fazer na perspectiva do programador. Ela define quais operações são suportadas (somar, subtrair, comparar, desviar), quais registradores existem e como são usados, como os endereços de memória são formados, e qual o formato binário de cada instrução. Em outras palavras, a ISA é o contrato entre o hardware e o software.

Esse contrato é extremamente importante porque permite que o mesmo conjunto de programas execute em processadores completamente diferentes por dentro, desde que ambos respeitem a mesma ISA. É por isso que um programa compilado para x86-64 roda tanto em um processador Intel de 2015 quanto em um AMD de 2024 — os transistores são completamente diferentes, mas a ISA é a mesma. Isso se chama compatibilidade binária.

Definição: Instruction Set Architecture (ISA)

A Instruction Set Architecture (ISA) é a especificação da interface entre o hardware de um processador e o software que nele executa. Ela define:

- O conjunto de instruções disponíveis e sua semântica (o que cada instrução faz)

- Os registradores visíveis ao programador (quantos, de qual largura, para que servem)

- Os tipos de dados suportados (inteiros de 8, 16, 32 bits; ponto flutuante; etc.)

- Os modos de endereçamento (como os operandos são especificados)

- O formato binário das instruções (quantos bits para cada campo)

- O modelo de memória (como o espaço de endereços é organizado)

- O mecanismo de interrupções e exceções

A ISA é distinta da implementação (organização) do processador. Dois chips com a mesma ISA podem ter desempenhos radicalmente diferentes — um pode ter pipeline de 20 estágios enquanto o outro tem 5.

A distinção entre ISA (arquitetura) e implementação (organização) que você estudou no Módulo 1 fica muito mais concreta agora. O PIC18F4550 e um processador ARM de alto desempenho são implementações radicalmente diferentes em termos de hardware interno, velocidade de clock e número de transistores. Mas cada um tem sua própria ISA, que define o que o programador enxerga. Mudar a implementação — usar transistores mais rápidos, adicionar mais estágios de pipeline — não quebra os programas existentes. Mudar a ISA, porém, exige recompilar todos os programas.

Existe ainda um nível abaixo da ISA que você encontrará nos módulos futuros: o microcode ou as micro-operações. Em processadores modernos como os Intel Core, as instruções da ISA x86 são internamente decompostas em operações mais simples antes de serem executadas. Mas isso é um detalhe de implementação — o programador nunca vê as micro-operações.

A Anatomia de Uma Instrução de Máquina

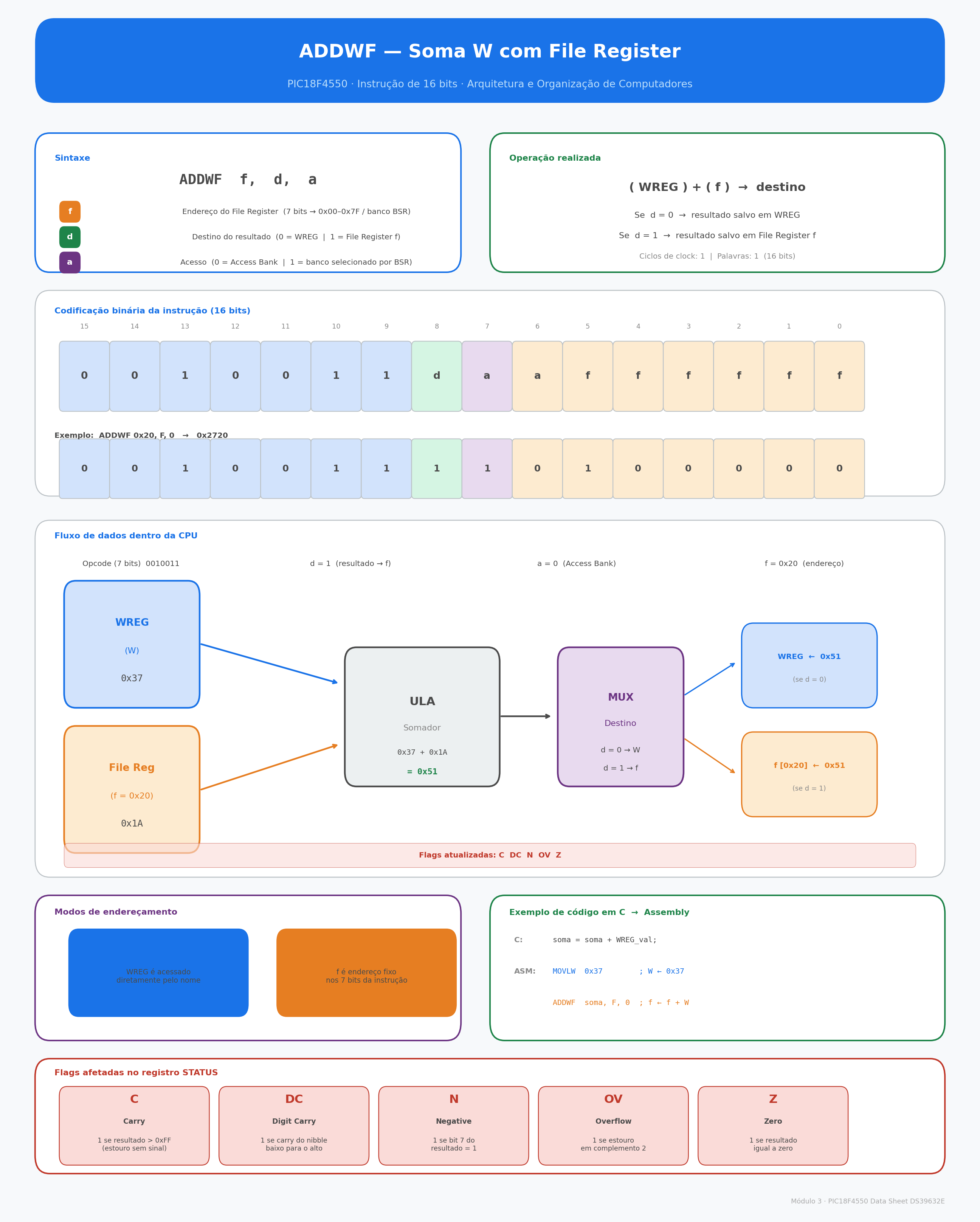

Quando você digita ADDWF soma, F em assembly para o PIC18F4550, ou quando o compilador gera o código equivalente a partir de soma += WREG;, o processador recebe um padrão de bits que codifica exatamente o que deve ser feito. Vamos dissecar essa instrução.

Toda instrução de máquina é composta por pelo menos dois elementos fundamentais: o opcode e os operandos.

O opcode (operation code) é o campo que especifica qual operação será realizada. É o “verbo” da instrução: somar, subtrair, mover dado, desviar para outro endereço, etc. No PIC18F4550, o opcode ocupa a parte mais significativa dos 16 bits da instrução.

Os operandos são os “substantivos” — os dados sobre os quais a operação atua. Uma instrução pode ter zero, um ou dois operandos, dependendo da arquitetura e do tipo de operação. Os operandos especificam onde os dados estão: num registrador, diretamente na instrução, em um endereço de memória, ou calculados a partir de uma base mais um deslocamento.

Exemplo: Decodificando uma Instrução do PIC18F4550

A instrução ADDWF f, d, a soma o conteúdo do registrador de trabalho W com o conteúdo do registrador de arquivo (File Register) f. O resultado vai para W (se d = 0) ou para f (se d = 1).

Formato binário da instrução (16 bits):

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

+---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+

| 0 | 0 | 1 | 0 | 0 | 1 | 1 | d | a | f | f | f | f | f | f | f |

+---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+- Bits 15-8: opcode

00100110didentifica a operaçãoADDWF - Bit

d: destino (0 = W, 1 = File Register) - Bit

a: acesso (0 = Access Bank, 1 = BSR selecionado) - Bits 6-0: endereço do File Register

f(7 bits → 128 posições)

Para ADDWF 0x20, F (somar W com endereço 0x20, resultado em 0x20):

0 0 1 0 0 1 1 1 0 0 1 0 0 0 0 0 = 0x2720O exemplo acima revela algo importante: o formato da instrução — como os bits são organizados — determina diretamente quanta flexibilidade o programador tem. Se você reservar apenas 7 bits para o endereço do operando, pode endereçar apenas 128 posições diretamente. Se quiser endereçar mais, precisará de outros mecanismos. Essa tensão entre o tamanho da instrução e a flexibilidade de endereçamento é uma das forças motrizes por trás das decisões de projeto de ISA.

Comprimento Fixo versus Variável

Uma decisão fundamental no projeto de uma ISA é se todas as instruções terão o mesmo tamanho em bits (comprimento fixo) ou se instruções diferentes podem ter tamanhos diferentes (comprimento variável).

O PIC18F4550 usa instruções de 16 bits para a grande maioria de suas instruções, com algumas instruções de desvio usando 32 bits (duas palavras de 16 bits). Essa é uma característica típica de arquiteturas RISC: instruções de comprimento fixo (ou quase fixo) simplificam enormemente o decodificador de instruções e facilitam o uso de pipeline.

A arquitetura x86, por outro lado, tem instruções que variam de 1 a 15 bytes. Isso permite maior densidade de código (programas menores), mas torna a decodificação muito mais complexa — o hardware precisa primeiro determinar onde termina uma instrução e começa a próxima, o que é um desafio significativo para quem projeta processadores de alto desempenho.

flowchart LR

subgraph RISC ["RISC - Comprimento Fixo (ex: PIC18F4550)"]

R1["Instrução 1<br/>16 bits"] --> R2["Instrução 2<br/>16 bits"] --> R3["Instrução 3<br/>16 bits"]

end

subgraph CISC ["CISC - Comprimento Variável (ex: x86)"]

C1["Instrução 1<br/>1 byte"] --> C2["Instrução 2<br/>3 bytes"] --> C3["Instrução 3<br/>6 bytes"]

end

Modos de Endereçamento: Como as Instruções Encontram Seus Dados

Você já sabe que uma instrução precisa especificar onde estão seus operandos. Mas “onde” pode significar coisas muito diferentes: o valor pode estar embutido diretamente na instrução, guardado em um registrador, em um endereço fixo de memória, ou calculado dinamicamente. Cada uma dessas possibilidades é um modo de endereçamento.

Os modos de endereçamento não são lista arbitrária de opções — cada um existe para suportar um padrão de programação específico. Vamos entender cada modo a partir da necessidade que ele resolve.

Endereçamento Imediato

A situação mais simples é quando o valor que você quer usar está disponível em tempo de compilação — é uma constante. Quando você escreve MOVLW 0x3F, você está dizendo ao PIC18F4550: “mova o valor 0x3F para o registrador W”. O operando (0x3F) está imediatamente disponível dentro da própria instrução — não há necessidade de acessar a memória.

Definição: Endereçamento Imediato

No endereçamento imediato, o operando é um valor constante embutido diretamente no campo de operando da instrução. Não é necessário acessar registradores ou memória para obtê-lo — o valor já está na instrução.

Vantagem: Extremamente rápido — o valor já está disponível quando a instrução é buscada da memória de programa.

Limitação: O valor deve ser conhecido em tempo de compilação e o tamanho máximo do operando é limitado pelos bits disponíveis no campo de imediato.

Exemplo no PIC18F4550:

O endereçamento imediato é perfeito para configurar registradores com valores de controle, inicializar contadores, ou aplicar máscaras de bits — operações que você realizará constantemente no Projeto Integrador. Quando você configura o TRISD para definir pinos como entrada ou saída, por exemplo:

Endereçamento Direto (Absoluto)

O endereçamento direto, também chamado de absoluto, é usado quando a instrução contém o endereço de memória onde o operando está armazenado — não o valor em si, mas o endereço. O processador usa esse endereço para buscar o dado na memória.

Pense nisso como um livro de receitas: o endereçamento imediato é quando a receita diz “adicione 2 colheres de sal”; o endereçamento direto é quando diz “adicione a quantidade de sal indicada na página 37”. Você precisa ir buscar a informação em outro lugar.

Definição: Endereçamento Direto

No endereçamento direto, o campo de operando da instrução contém o endereço da posição de memória (ou registrador de arquivo, no caso do PIC) onde o operando está armazenado. O processador precisa realizar um acesso à memória para obter o valor.

Vantagem: Permite acessar qualquer posição do espaço de endereçamento suportado pelo campo de endereço.

Limitação: O endereço deve ser conhecido em tempo de compilação (variáveis globais e estáticas); não serve para ponteiros ou arrays dinâmicos.

Exemplo no PIC18F4550:

No PIC18F4550, a maioria das instruções que operam sobre registradores de arquivo (File Registers) usa endereçamento direto. Quando você tem uma variável global uint8_t contador;, o compilador reserva um endereço fixo para ela na RAM, e as instruções que a acessam usam esse endereço diretamente.

Endereçamento por Registrador

Em vez de buscar o dado na memória, o operando pode estar em um registrador do processador. O endereçamento por registrador especifica qual registrador contém o dado, e como os registradores estão dentro do próprio processador (não na memória externa), o acesso é muito mais rápido.

Definição: Endereçamento por Registrador

No endereçamento por registrador, o campo de operando da instrução especifica um registrador (identificado por um número ou nome) que contém o operando. O acesso é extremamente rápido porque os registradores fazem parte do próprio processador.

Vantagem: Velocidade máxima — nenhum acesso à memória RAM externa é necessário.

Limitação: O número de registradores é limitado pelo espaço de bits disponível na instrução para identificá-los.

Exemplo no PIC18F4550: O PIC18 tem um único registrador de trabalho principal (W) e acesso a registradores de propósito especial (SFRs). A instrução ADDWF f, W usa W como registrador de destino.

Arquiteturas com muitos registradores de uso geral — como o ARM (16 registradores de 32 bits) ou o RISC-V (32 registradores) — se beneficiam muito do endereçamento por registrador. O compilador tenta manter as variáveis mais utilizadas nos registradores o máximo possível, evitando acessos à memória RAM que são mais lentos.

O PIC18F4550 tem uma filosofia diferente: ao invés de muitos registradores de uso geral, ele tem 128 bytes de Access Bank mapeados diretamente no espaço de endereços, acessíveis em um único ciclo. Isso dá ao programador mais “espaço de trabalho” rápido, mas com semântica ligeiramente diferente de um banco de registradores clássico.

Endereçamento Indireto

Chegamos a um modo de endereçamento mais poderoso — e mais utilizado em programação de alto nível do que você pode imaginar. No endereçamento indireto, a instrução não contém o endereço do dado diretamente; ela contém o endereço de um registrador ou posição de memória que por sua vez contém o endereço do dado.

É como um sistema de caixas de correio: o endereçamento direto seria “o pacote está na caixa 42”; o endereçamento indireto seria “na caixa 10 há um papel que diz onde o pacote está”.

Definição: Endereçamento Indireto

No endereçamento indireto, o campo da instrução especifica um registrador (ou endereço de memória) que contém o endereço efetivo do operando. São necessários dois acessos para obter o dado: primeiro para ler o endereço, depois para ler o dado em si.

Vantagem: Permite que o endereço efetivo seja calculado em tempo de execução — fundamental para implementar ponteiros, passar arrays como parâmetros de funções, e estruturas de dados dinâmicas.

Exemplo no PIC18F4550 (registradores FSR):

O registrador INDF0 não é uma posição de memória real — acessá-lo faz o hardware ler o endereço guardado em FSR0 e retornar o dado naquele endereço.

O endereçamento indireto é o que permite que ponteiros funcionem em C. Quando você escreve *ptr = valor;, o compilador gera instrução de endereçamento indireto: “escreva valor no endereço guardado em ptr”. Sem esse modo de endereçamento, ponteiros simplesmente não existiriam como conceito.

O PIC18F4550 tem três pares de registradores de endereçamento indireto: FSR0/INDF0, FSR1/INDF1 e FSR2/INDF2. Cada par age como um ponteiro de 12 bits, capaz de endereçar toda a RAM do microcontrolador. As variantes POSTINC, POSTDEC, PREINC e PLUSW oferecem modos de acesso com auto-incremento, auto-decremento e indexação — como veremos a seguir.

Endereçamento Indexado

O endereçamento indexado combina um endereço base com um deslocamento (offset) para calcular o endereço efetivo. É o modo de endereçamento mais natural para acessar elementos de arrays e campos de estruturas.

Definição: Endereçamento Indexado

No endereçamento indexado, o endereço efetivo é calculado somando um endereço base (armazenado em um registrador) com um deslocamento (offset), que pode ser um valor imediato na instrução ou o conteúdo de outro registrador.

\text{Endereço Efetivo} = \text{Base} + \text{Deslocamento}

Vantagem: Permite acesso eficiente a elementos sequenciais de arrays e campos de estruturas com código compacto.

Exemplo no PIC18F4550 (PLUSW0):

O endereçamento indexado é exatamente o que acontece quando você escreve buffer[i] em C. O compilador gera código que coloca o endereço base do array em um registrador e usa o índice i como deslocamento. No PIC18F4550, o modo PLUSW usa o conteúdo do registrador W como deslocamento em relação ao FSR correspondente.

flowchart LR

subgraph Modos ["Modos de Endereçamento: Resumo Visual"]

IM["**Imediato**<br/>Operando = Constante<br/>na instrução<br/>ex: MOVLW 0x3F"]

DIR["**Direto**<br/>Operando = Mem[endereço]<br/>endereço na instrução<br/>ex: MOVF contador, W"]

REG["**Registrador**<br/>Operando = Registrador<br/>ex: ADDWF f, W"]

IND["**Indireto**<br/>Operando = Mem[Reg]<br/>Reg guarda o endereço<br/>ex: MOVF INDF0, W"]

IDX["**Indexado**<br/>Operando = Mem[Base + Offset]<br/>ex: MOVF PLUSW0, W"]

end

Por Que Tantos Modos de Endereçamento?

Você pode estar se perguntando: por que tanta variedade? A resposta está nos padrões de acesso que surgem naturalmente na programação:

As variáveis locais de uma função — aquelas que existem apenas enquanto a função executa — são armazenadas na pilha (stack) em deslocamentos fixos em relação ao ponteiro de pilha. Isso é endereçamento indexado relativo ao stack pointer. As variáveis globais têm endereços fixos conhecidos em tempo de compilação — endereçamento direto. Os ponteiros em C são, por definição, endereçamento indireto. Os elementos de arrays acessados por índice variável são endereçamento indexado. E as constantes embutidas no código são endereçamento imediato.

Portanto, uma ISA com mais modos de endereçamento permite que o compilador gere código mais eficiente para cada padrão de acesso. A contrapartida é que o hardware de decodificação fica mais complexo.

CISC e RISC: Duas Filosofias de Projeto

Com a anatomia das instruções e os modos de endereçamento em mente, estamos prontos para entender um dos debates mais importantes na história da arquitetura de computadores: a disputa entre CISC e RISC.

A Origem do CISC

Nos anos 1960 e 1970, a memória era extremíssimamente cara. Um kilobyte de RAM podia custar dezenas de dólares. Nesse contexto, reduzir o tamanho dos programas era uma prioridade econômica real. A solução foi criar processadores com instruções cada vez mais complexas e poderosas: uma única instrução de máquina poderia realizar o que em linguagem de alto nível levaria várias linhas.

Por exemplo, o processador VAX da DEC, um clássico da era CISC, tinha uma instrução POLYF que calculava um polinômio inteiro — múltiplas multiplicações e adições em uma única instrução de máquina. A instrução EDITPC manipulava strings de caracteres com formatação complexa. Com instruções assim, os programas ficavam menores (menos bytes) e, teoricamente, faziam mais trabalho por instrução executada.

Essa abordagem ficou conhecida como CISC — Complex Instruction Set Computer. Características típicas de arquiteturas CISC:

- Instruções de comprimento variável (de 1 a 15 bytes, no caso do x86)

- Grande número de instruções diferentes (centenas ou até milhares de opcodes)

- Muitos modos de endereçamento (incluindo modos que acessam memória diretamente em operações aritméticas)

- Instruções que executam operações complexas em múltiplos ciclos

- Relativamente poucos registradores de uso geral

A arquitetura x86, usada nos PCs desde 1978 e ainda dominante em servidores e desktops, é o exemplo mais proeminente de CISC no mundo atual.

Exemplo: Instrução CISC (x86)

A instrução x86 IMUL r64, m64 multiplica um registrador de 64 bits pelo conteúdo de um endereço de memória em uma única instrução. Ela:

- Calcula o endereço de memória (potencialmente com indexação complexa)

- Lê o dado de 64 bits da memória

- Multiplica pelo registrador especificado

- Escreve o resultado no registrador

Tudo isso em uma única instrução que pode ter até 9 bytes de tamanho.

A Revolução RISC

Na virada dos anos 1970 para 1980, pesquisadores da IBM e depois da UC Berkeley e Stanford fizeram uma descoberta surpreendente: apesar de toda a sofisticação das arquiteturas CISC, os programas reais usavam um conjunto muito pequeno de instruções a maior parte do tempo. As instruções complexas eram raramente executadas. E pior: as instruções complexas eram difíceis de implementar eficientemente em hardware — elas ocupavam a maior parte da área do chip mas contribuíam pouco para o desempenho real.

Essa observação levou a uma ideia radical: e se reduzíssemos o conjunto de instruções apenas às mais frequentemente usadas, mas as tornássemos extremamente rápidas? O resultado foi a filosofia RISC — Reduced Instruction Set Computer.

Definição: RISC — Princípios Fundamentais

As arquiteturas RISC foram projetadas em torno de alguns princípios centrais, formulados originalmente pelos projetos RISC da UC Berkeley e MIPS de Stanford no início dos anos 1980:

1. Instruções simples e uniformes: Cada instrução realiza uma única operação elementar. A complexidade é alcançada pela combinação de muitas instruções simples.

2. Arquitetura load-store: Apenas instruções especiais de carga (load) e armazenamento (store) acessam a memória. Todas as outras operações aritméticas e lógicas trabalham exclusivamente sobre registradores.

3. Comprimento fixo de instruções: Todas as instruções têm o mesmo tamanho em bits. Isso simplifica drasticamente o decodificador e facilita o pipeline.

4. Grande banco de registradores: Com muitos registradores disponíveis, o compilador pode manter mais variáveis “quentes” nos registradores, evitando acessos à memória.

5. Uma instrução por ciclo: O objetivo é que cada instrução execute em exatamente um ciclo de clock (ou próximo disso), tornando o pipeline previsível e eficiente.

O impacto do RISC foi enorme. Os processadores MIPS (que você talvez conheça dos roteadores domésticos), SPARC (servidores Sun), PowerPC (Macs até 2006), e especialmente o ARM (praticamente todos os smartphones do mundo) são derivados dessa filosofia.

O PIC18F4550 como Exemplo RISC

O PIC18F4550 é uma arquitetura de 8 bits que adota vários princípios RISC, embora adaptados para um microcontrolador de baixo custo e baixo consumo:

Ele tem 75 instruções — um conjunto reduzido e coeso. A maioria executa em apenas 1 ciclo de clock (4 períodos de oscilador, no jargão do PIC). Instruções de desvio que envolvem mudança de fluxo de programa levam 2 ciclos. O formato de instrução é predominantemente de 16 bits (comprimento fixo). E o modelo de programação é simples: um registrador de trabalho central (W) que age como acumulador em quase todas as operações.

CISC vs. RISC: Uma Comparação Direta

| Característica | CISC (ex: x86) | RISC (ex: PIC18, ARM) |

|---|---|---|

| Número de instruções | Centenas/milhares | Dezenas/poucos centos |

| Comprimento das instruções | Variável (1–15 bytes) | Fixo (tipicamente 16 ou 32 bits) |

| Modos de endereçamento | Muitos (>10) | Poucos (4–6) |

| Acesso à memória | Qualquer instrução | Apenas load/store |

| Ciclos por instrução | 1 a dezenas | 1 (maioria das instruções) |

| Registradores de uso geral | Poucos (x86-32: 8; x86-64: 16) | Muitos (ARM: 16; RISC-V: 32) |

| Complexidade do decodificador | Alta | Baixa |

| Exemplos | Intel x86, Motorola 68k, VAX | ARM, MIPS, RISC-V, PIC18, AVR |

O Mundo Real: CISC com Coração RISC

Se o RISC é mais eficiente, por que o x86 ainda domina os computadores pessoais? A resposta é a compatibilidade binária. Bilhões de programas foram compilados para x86 ao longo de décadas. Descartá-los seria economicamente inviável.

A solução elegante que Intel e AMD adotaram foi manter a ISA x86 (CISC) para compatibilidade, mas implementar internamente o processador com um núcleo RISC. As instruções x86 complexas são decodificadas e traduzidas internamente em micro-operações simples do tipo RISC, que então executam no núcleo de alto desempenho. O programador enxerga CISC; o hardware executa RISC.

Isso ilustra perfeitamente a distinção arquitetura/organização que você estudou no Módulo 1: a ISA (o que o programador vê) permanece CISC; a implementação interna (o que o engenheiro de hardware projeta) é RISC.

O Conjunto de Instruções do PIC18F4550

Chegou a hora de conhecer em detalhes a ISA que você vai usar durante todo o Projeto Integrador. O PIC18F4550 possui 75 instruções, organizadas em cinco categorias funcionais. Você não precisa memorizar todas agora — aprenderá as mais importantes conforme o projeto avança. Mas é essencial compreender a estrutura geral e saber onde encontrar o que precisa.

Organização do Banco de Registradores

Antes de explorar as instruções, você precisa entender o espaço de endereços de dados do PIC18F4550. Diferentemente de arquiteturas com banco de registradores separado, o PIC18 usa um modelo onde toda a memória de dados (RAM) é mapeada em um espaço de endereços linear de 12 bits (4096 posições), e as instruções operam diretamente sobre esses endereços.

flowchart TD

subgraph Mem ["Mapa de Memória de Dados - PIC18F4550"]

SFR["Endereços 0xF80–0xFFF<br/><b>SFRs - Special Function Registers</b><br/>WREG, STATUS, TRISD, PORTD,<br/>INTCON, TMR0, ADCON0, ..."]

RAM["Endereços 0x000–0xEFF<br/><b>General Purpose RAM</b><br/>Suas variáveis ficam aqui<br/>(1536 bytes no PIC18F4550)"]

end

W["Registrador W (Acumulador)<br/>Implícito na maioria das instruções"]

PC["Program Counter (PC)<br/>21 bits - endereço na Flash"]

W --> SFR

RAM -.->|"acessado via endereço"| SFR

O registrador W (Working Register) é o acumulador central do PIC18. Ele participa implicitamente de quase todas as operações aritméticas e lógicas. Quando você soma dois números, um deles sempre está em W. O resultado pode ir para W ou para o registrador de arquivo especificado.

O registrador STATUS contém os flags de condição: Z (Zero), N (Negative), OV (Overflow), C (Carry) e DC (Digit Carry). Esses flags são atualizados pelas instruções aritméticas e lógicas e são lidos pelas instruções de desvio condicional.

Categoria 1: Instruções de Operações sobre Bytes

São as instruções que realizam operações sobre registradores de arquivo (File Registers) de 8 bits. O destino pode ser o próprio registrador (bit d = 1) ou o registrador W (bit d = 0).

Instruções de Bytes — Principais Exemplos

| Instrução | Operação | Ciclos | Flags afetados |

|---|---|---|---|

ADDWF f, d, a |

d = W + f | 1 | C, DC, Z, OV, N |

SUBWF f, d, a |

d = f − W | 1 | C, DC, Z, OV, N |

ANDWF f, d, a |

d = W AND f | 1 | Z, N |

IORWF f, d, a |

d = W OR f | 1 | Z, N |

XORWF f, d, a |

d = W XOR f | 1 | Z, N |

MOVWF f, a |

f = W | 1 | — |

MOVF f, d, a |

d = f | 1 | Z, N |

INCF f, d, a |

d = f + 1 | 1 | C, DC, Z, OV, N |

DECF f, d, a |

d = f − 1 | 1 | C, DC, Z, OV, N |

CLRF f, a |

f = 0; Z = 1 | 1 | Z |

COMF f, d, a |

d = NOT f | 1 | Z, N |

RLCF f, d, a |

Rotação esq. com carry | 1 | C, Z, N |

RRCF f, d, a |

Rotação dir. com carry | 1 | C, Z, N |

Nota: f = File Register (endereço), d = destino (W se 0, f se 1), a = banco de acesso (0 = Access Bank, 1 = BSR)

Vamos ver um exemplo prático. Suponha que você quer implementar uma rotina para acender LEDs conectados ao PORTD do kit ACEPIC PRO V8.2 de forma alternada — acende os pares e apaga os ímpares, depois inverte.

Categoria 2: Instruções de Operações sobre Bits

Uma das características mais convenientes do PIC18 é a capacidade de acessar bits individuais de qualquer registrador de arquivo diretamente, sem precisar de máscaras.

Instruções de Bits — Principais Exemplos

| Instrução | Operação | Ciclos |

|---|---|---|

BSF f, b, a |

Seta bit b de f (f[b] = 1) | 1 |

BCF f, b, a |

Limpa bit b de f (f[b] = 0) | 1 |

BTG f, b, a |

Inverte (toggle) bit b de f | 1 |

BTFSS f, b, a |

Testa bit; pula próxima se bit = 1 | 1 ou 2 |

BTFSC f, b, a |

Testa bit; pula próxima se bit = 0 | 1 ou 2 |

Exemplo: Para acender apenas o LED no pino RD2:

Essas instruções eliminam completamente a necessidade de operações de mascaramento manual para manipulação de bits individuais. Em arquiteturas sem esse recurso, acender um LED exigiria: ler o registrador, aplicar OR com a máscara, escrever o resultado. No PIC18, é uma única instrução. Isso é muito conveniente para sistemas embarcados onde você controla pinos de I/O individualmente.

Categoria 3: Instruções de Operações com Literais

São as instruções que operam com valores constantes embutidos diretamente na instrução — endereçamento imediato, em outras palavras.

Instruções com Literais — Exemplos

| Instrução | Operação | Ciclos |

|---|---|---|

MOVLW k |

W = k (literal de 8 bits) | 1 |

ADDLW k |

W = W + k | 1 |

SUBLW k |

W = k − W | 1 |

ANDLW k |

W = W AND k | 1 |

IORLW k |

W = W OR k | 1 |

XORLW k |

W = W XOR k | 1 |

MULLW k |

PRODH:PRODL = W × k | 1 |

LFSR FSR, k |

FSR = k (literal de 12 bits) | 2 |

Onde k é o valor literal (constante imediata).

Uma instrução especialmente poderosa é MULLW k, que multiplica W por um literal de 8 bits e coloca o resultado de 16 bits nos registradores PRODH (byte alto) e PRODL (byte baixo). Isso é possível porque o PIC18F4550 tem um multiplicador de hardware de 8×8 bits, algo que microcontroladores mais antigos da família PIC não possuíam. Com ele, uma multiplicação completa leva apenas 1 ciclo — compare com as dezenas de ciclos que uma multiplicação por software levava nas famílias PIC16 e PIC12.

Categoria 4: Instruções de Controle de Fluxo

O programa não executa linearmente do início ao fim — ele precisa tomar decisões, repetir trechos e chamar sub-rotinas. Essas operações são realizadas pelas instruções de controle de fluxo.

Instruções de Controle de Fluxo

| Instrução | Operação | Ciclos |

|---|---|---|

GOTO k |

PC = k (desvio incondicional) | 2 |

BRA n |

PC = PC + 2 + 2n (desvio relativo ±1 KB) | 2 |

BZ n |

Desvia se Z = 1 (resultado zero) | 1 ou 2 |

BNZ n |

Desvia se Z = 0 (resultado não zero) | 1 ou 2 |

BC n |

Desvia se C = 1 (carry) | 1 ou 2 |

BNC n |

Desvia se C = 0 (não carry) | 1 ou 2 |

BN n |

Desvia se N = 1 (negativo) | 1 ou 2 |

BOV n |

Desvia se OV = 1 (overflow) | 1 ou 2 |

CALL k |

Empilha PC; PC = k (chamada de sub-rotina) | 2 |

RETURN |

Desempilha e retorna da sub-rotina | 2 |

RETLW k |

Retorna com W = k | 2 |

RETFIE |

Retorna de interrupção | 2 |

DECFSZ f, d, a |

Decrementa f; pula se resultado = 0 | 1 ou 2 |

INCFSZ f, d, a |

Incrementa f; pula se resultado = 0 | 1 ou 2 |

As instruções de desvio condicional verificam os flags do registrador STATUS. Por exemplo, BZ n desvia para PC + 2 + 2n se o flag Z (Zero) estiver setado — o que acontece quando uma operação aritmética ou lógica gerou resultado zero. Isso é exatamente o que ocorre quando você escreve if (contador == 0) em C.

O diagrama abaixo mostra como uma estrutura for em C é traduzida para assembly usando essas instruções:

flowchart TD

INIT["MOVLW 10<br/>MOVWF contador<br/>(inicializa contador = 10)"]

LOOP_START["início do laço<br/>(rótulo loop_start)"]

BODY["... corpo do laço ...<br/>(instruções que fazem o trabalho)"]

DECR["DECFSZ contador, F<br/>(decrementa; pula próxima se zero)"]

GOTO_LOOP["GOTO loop_start<br/>(volta para início)"]

AFTER["... código após o laço ..."]

INIT --> LOOP_START

LOOP_START --> BODY

BODY --> DECR

DECR -->|"contador ≠ 0<br/>(não pula)"| GOTO_LOOP

DECR -->|"contador = 0<br/>(pula o GOTO)"| AFTER

GOTO_LOOP --> LOOP_START

A instrução DECFSZ é elegante: ela decrementa o registrador e em uma única operação testa se o resultado é zero. Se for, a próxima instrução é pulada. Isso é um padrão RISC clássico — combinar a operação (decremento) com o teste de condição para economizar uma instrução de branch adicional.

Categoria 5: Instruções de Controle do Processador

A última categoria inclui instruções que controlam o próprio estado do processador: dormir para economizar energia, desabilitar interrupções, operar diretamente na pilha de hardware, etc.

Instruções de Controle do Processador

| Instrução | Operação |

|---|---|

NOP |

Nenhuma operação (1 ciclo de espera) |

SLEEP |

Entra em modo de baixo consumo |

CLRWDT |

Limpa o Watchdog Timer |

RESET |

Reinicia o microcontrolador por software |

PUSH |

Empilha o PC na pilha de hardware |

POP |

Desempilha da pilha de hardware |

A instrução NOP (No Operation) pode parecer inútil à primeira vista, mas tem usos práticos importantes: gerar atrasos precisos de tempo, preencher posições para alinhamento de código, e servir como marcador em pipelines (em processadores mais complexos).

Correlacionando C e Assembly: O Que Acontece Quando Você Compila?

Agora que você conhece as instruções do PIC18F4550, vamos fazer algo muito valioso: examinar o que o compilador XC8 gera para construções comuns em C. Isso vai revelar os modos de endereçamento em ação e ajudá-lo a estimar o custo em ciclos de diferentes trechos de código.

Variáveis Locais versus Globais

Exemplo: Tipos de Variáveis e Seus Modos de Endereçamento

Assembly gerado (aproximado):

Para o XC8, variáveis locais de funções simples frequentemente recebem endereços fixos (static allocation) em vez de serem empilhadas, dado o tamanho reduzido da RAM e a ausência de recursão típica em microcontroladores.

Acesso a Arrays: Endereçamento Indexado em Ação

; Acesso por índice FIXO (índice 3 conhecido em compilação)

; O compilador calcula o endereço: base + 3

MOVLW 25

MOVWF (temperaturas + 3), ACCESS ; endereço = base + deslocamento fixo

; Acesso por índice VARIÁVEL (indice calculado em tempo de execução)

; O compilador usa FSR + modo PLUSW ou POSTINC

MOVF indice, W ; W = valor do índice

LFSR FSR0, temperaturas ; FSR0 = endereço base do array

MOVF PLUSW0, W ; W = temperaturas[W] (indexado!)

MOVLW 30

MOVWF PLUSW0 ; temperaturas[W] = 30Esse exemplo é muito revelador. Para um índice fixo (conhecido em tempo de compilação), o compilador simplesmente calcula o endereço final e usa endereçamento direto. Para um índice variável, o compilador precisa usar o modo indexado via FSR + PLUSW. Isso é mais custoso em ciclos e instruções — razão pela qual o compilador, quando possível, “desfaz” laços (loop unrolling) ou usa índices constantes.

Chamadas de Função: A Pilha em Ação

Quando você chama uma função em C, ocorre uma série de operações coordenadas envolvendo a pilha de hardware do PIC18F4550:

sequenceDiagram

participant Caller as Função chamadora

participant Stack as Pilha de Hardware

participant Callee as Função chamada

Caller->>Stack: CALL: empilha PC+2 (endereço de retorno)

Caller->>Callee: Transfere controle para a função

Note over Callee: Executa o corpo da função

Callee->>Stack: RETURN: desempilha endereço de retorno

Stack->>Caller: PC = endereço de retorno

Note over Caller: Continua execução após o CALL

O PIC18F4550 tem uma pilha de hardware de 31 níveis (31 endereços de retorno podem ser empilhados). Isso significa que você pode ter no máximo 31 níveis de aninhamento de chamadas de função. Para a maioria das aplicações em microcontroladores, isso é suficiente. Mas se você tentar usar recursão profunda, descobrirá que a pilha transborda — sem aviso!

O PIC18F4550 em Perspectiva: Uma Arquitetura Harvard Modificada

Antes de partir para os exemplos do Projeto Integrador, há um detalhe arquitetural importante que você notou no Módulo 1 e que agora faz ainda mais sentido: o PIC18F4550 usa uma arquitetura Harvard modificada.

Você se lembra que a arquitetura Harvard separa a memória de programa e a memória de dados em barramentos físicos distintos. No PIC18F4550:

- A memória de programa (Flash de 32 KB) é acessada por um barramento de 21 bits, e as instruções são buscadas em palavras de 16 bits.

- A memória de dados (RAM de 2 KB + SFRs) é acessada por um barramento separado de 12 bits, e os dados são bytes de 8 bits.

A palavra “modificada” vem do fato de que o PIC18 possui uma instrução especial — TBLRD (Table Read) — que permite ler dados da memória de programa como se fossem dados. Isso é útil para armazenar tabelas de valores constantes (como tabelas de seno/cosseno ou mensagens de texto para o LCD) na Flash, economizando a preciosa RAM.

Exemplo: Tabela de Constantes na Memória de Programa

/*

* Armazena uma tabela de valores de seno quantizados (0-255)

* na memória de programa (Flash) — economia de RAM

* PIC18F4550 - Módulo 3

*/

#include <xc.h>

#include <stdint.h>

/* Palavra-chave 'const' instrui o compilador a colocar na Flash */

/* Palavra-chave 'rom' é específica do XC8 para PIC */

const uint8_t tabela_seno[16] = {

128, 178, 218, 245, 255, 245, 218, 178,

128, 78, 38, 11, 0, 11, 38, 78

};

/* Esta tabela ocupa 16 bytes na Flash, não na RAM */

void main(void) {

uint8_t i;

uint8_t valor_seno;

for (i = 0; i < 16; i++) {

/* O compilador gera TBLRD para acessar a Flash */

valor_seno = tabela_seno[i];

/* Usa o valor (ex: envia para DAC ou PWM) */

PORTD = valor_seno;

}

while(1);

}Essa capacidade de usar a Flash como repositório de dados constantes é extremamente valiosa. A RAM do PIC18F4550 tem apenas 2 KB — pouquíssimo para guardar tabelas grandes. A Flash, com seus 32 KB, oferece muito mais espaço. Para aplicações como displays de caracteres customizados, mapas de conversão de sensores ou mensagens de texto, essa técnica é indispensável.

Conectando ao Projeto Integrador

Agora que você tem uma compreensão sólida do conjunto de instruções e dos modos de endereçamento, vamos ver como isso se conecta diretamente às tarefas do seu Projeto Integrador neste módulo.

Tarefa 1: Analisando o Assembly das Suas Funções

No Módulo 2, você implementou rotinas de conversão numérica e operações aritméticas. Neste módulo, você vai usar o MPLAB X para examinar o assembly que o compilador XC8 gerou para essas funções. O processo é revelador.

Para fazer isso no MPLAB X: após compilar o projeto, acesse Window → Disassembly Listing. Você verá seu código C intercalado com o assembly gerado.

Exemplo: Analisando Assembly de uma Função do Módulo 2

Suponha que você implementou a função decimal_para_binario no Módulo 2. Ao examinar o assembly, você pode encontrar algo como:

; Trecho do assembly gerado para o laço for (i = 7; i >= 0; i--)

;

_decimal_para_binario:

; Configura parâmetros...

MOVLW 8 ; contador de 8 iterações

MOVWF _count ; armazena localmente

_loop:

; Testa o bit atual

RLNCF _valor, W ; rotaciona para verificar bit MSB

BC _bit_um ; se bit = 1, vai para bit_um

MOVLW '0'

BRA _escreve

_bit_um:

MOVLW '1'

_escreve:

; Escrita no buffer (endereçamento indireto via FSR)

MOVWF POSTINC0 ; escreve e incrementa ponteiro (FSR0++)

DECFSZ _count, F ; decrementa contador; pula se zero

BRA _loop ; volta ao início

; Termina string

CLRF POSTINC0 ; null terminator '\0'

RETURNO que você aprende: - O laço usa DECFSZ + BRA — padrão clássico de laço contado no PIC18 - A escrita no buffer usa POSTINC0 (endereçamento indireto com auto-incremento) - O teste de bit usa rotação e desvio condicional BC - Cada iteração do laço consome aproximadamente 5–7 ciclos

Tarefa 2: Implementando uma Função Crítica em Assembly

Para aprender a escrever assembly diretamente, você vai implementar uma função de desempenho crítico: a soma de elementos de um vetor. Primeiro em C, depois comparar com versão em assembly otimizado.

/*

* Soma de vetor em C - versão de referência

* PIC18F4550 - Módulo 3 - Projeto Integrador

*/

#include <xc.h>

#include <stdint.h>

uint8_t leituras[8]; /* vetor global de leituras do sensor */

/* Retorna a soma dos 8 elementos */

uint16_t soma_vetor(void) {

uint8_t i;

uint16_t soma = 0;

for (i = 0; i < 8; i++) {

soma += leituras[i];

}

return soma;

};************************************************************

; soma_vetor_asm: soma os 8 bytes do vetor 'leituras'

; Retorna resultado de 16 bits em WREG (byte baixo) e

; registrador _soma_high (byte alto)

; Ciclos: ~35 ciclos no total (versus ~50 da versão C)

;************************************************************

soma_vetor_asm:

LFSR FSR0, _leituras ; FSR0 = base do vetor

CLRF _soma_low ; soma_low = 0

CLRF _soma_high ; soma_high = 0

MOVLW 8 ; contador de 8 elementos

MOVWF _counter

soma_loop:

MOVF POSTINC0, W ; W = leituras[i]; FSR0++

ADDWF _soma_low, F ; soma_low += W

BTFSS STATUS, C ; houve carry?

BRA soma_no_carry

INCF _soma_high, F ; soma_high++ (propagação do carry)

soma_no_carry:

DECFSZ _counter, F ; decrementa; pula se zero

BRA soma_loop ; próximo elemento

MOVF _soma_low, W ; retorna byte baixo em W

RETURN/*

* Medição de desempenho usando Timer0

* PIC18F4550 @ 8 MHz → 1 ciclo de instrução = 500 ns

*

* Resultado típico (para 8 elementos):

* - Versão C (compilador): ~50 ciclos ≈ 25 µs

* - Versão Assembly: ~35 ciclos ≈ 17,5 µs

* - Melhoria: ~30% mais rápido

*

* Para aplicações com leituras frequentes de sensores,

* essa diferença pode ser significativa!

*/Tarefa 3: Documentando Modos de Endereçamento

A terceira tarefa do Projeto Integrador para este módulo pede que você produza uma tabela correlacionando padrões de código C com os modos de endereçamento que o compilador usa. Isso solidifica sua compreensão de como a teoria se mapeia para a prática.

Tabela de Correlação: C → Modo de Endereçamento → Assembly

| Padrão em C | Modo de Endereçamento | Instrução Assembly Típica |

|---|---|---|

variavel = 42; |

Imediato | MOVLW 42; MOVWF variavel |

variavel = outra; |

Direto | MOVF outra, W; MOVWF variavel |

*ptr = valor; |

Indireto (FSR/INDF) | MOVF valor, W; MOVWF INDF0 |

array[i] (i variável) |

Indexado (FSR/PLUSW) | LFSR FSR0, array; MOVF PLUSW0, W |

array[3] (índice fixo) |

Direto | MOVF (array+3), W |

PORTDbits.RD2 = 1; |

Direto + Bit | BSF PORTD, 2 |

contador++; |

Direto (in-place) | INCF contador, F |

if (flag == 0) |

Direto + Condicional | MOVF flag, F; BNZ ... |

Modos de Endereçamento Avançados do PIC18F4550

Para completar sua compreensão, vamos explorar as variantes de endereçamento indireto que o PIC18F4550 oferece através dos seus três pares FSR/INDF.

Variantes de Endereçamento Indireto no PIC18F4550

O PIC18 oferece seis variantes de acesso indireto para cada FSR (substituindo INDF0 com INDF1 ou INDF2 para os outros pares):

| Operando | Comportamento | Uso típico |

|---|---|---|

INDF0 |

Acesso indireto simples. FSR0 não muda. | Leitura/escrita em posição fixa via ponteiro |

POSTINC0 |

Acesso, depois FSR0++ | Percorrer array para frente (como *ptr++) |

POSTDEC0 |

Acesso, depois FSR0– | Percorrer array para trás (como *ptr--) |

PREINC0 |

FSR0++, depois acesso | Acesso pós-incremento (como *++ptr) |

PLUSW0 |

Acessa endereço FSR0 + W | Acesso indexado com offset variável |

Exemplo prático — copiar vetor de forma eficiente:

; Copia 'n' bytes de 'origem' para 'destino'

; Usando POSTINC para ambos os ponteiros

LFSR FSR0, origem ; FSR0 = ponteiro origem

LFSR FSR1, destino ; FSR1 = ponteiro destino

MOVLW n ; contador

MOVWF contador

copia_loop:

MOVF POSTINC0, W ; W = *FSR0; FSR0++

MOVWF POSTINC1 ; *FSR1 = W; FSR1++

DECFSZ contador, F

BRA copia_loopEsse padrão de cópia com POSTINC é extremamente eficiente: dois acessos à memória e o incremento de ambos os ponteiros acontecem implicitamente, sem instruções extras. Em C, o equivalente *dst++ = *src++; gera exatamente esse padrão.

O Modelo de Memória do PIC18F4550 em Detalhe

Para usar com segurança os modos de endereçamento que você aprendeu, precisa entender como o espaço de memória do PIC18F4550 é organizado. Essa compreensão é essencial para interpretar mensagens de erro do compilador, depurar problemas de ponteiros e escrever código que se beneficie do banco de acesso rápido.

O Espaço de Endereços de Dados

O PIC18F4550 organiza sua memória de dados em um espaço de endereçamento de 12 bits, cobrindo até 4096 posições (0x000 a 0xFFF). Desse espaço, 2048 bytes são RAM de uso geral (General Purpose Registers, ou GPRs) e as posições superiores são os registradores de função especial (SFRs).

block-beta

columns 1

block:SFR["SFRs - Special Function Registers<br/>0xF80 a 0xFFF (128 bytes)<br/>WREG, STATUS, TRISD, PORTD, TMR0, ADCON..."]

block:RAM3["GPR Bank 3 - 0x300 a 0x3FF (256 bytes)"]

block:RAM2["GPR Bank 2 - 0x200 a 0x2FF (256 bytes)"]

block:RAM1["GPR Bank 1 - 0x100 a 0x1FF (256 bytes)"]

block:RAM0["GPR Bank 0 - 0x000 a 0x0FF (256 bytes)"]

O espaço de endereçamento é dividido em bancos de 256 bytes cada. As instruções que usam endereçamento direto com campos de 7 bits só podem endereçar 128 posições — as instruções de byte do PIC18 usam o campo a (bit de acesso) junto com o registro BSR (Bank Select Register) para selecionar qual banco está ativo.

O Access Bank é uma conveniência especial: os 96 bytes inferiores do banco 0 (endereços 0x000 a 0x05F) e os 160 bytes superiores de SFRs (0xF60 a 0xFFF) formam o Access Bank, acessível sem necessidade de mudar o BSR. Isso significa que, usando a = 0 nas instruções, você acessa essas posições em 1 ciclo, sem overhead de seleção de banco. O compilador XC8 aproveita isso colocando variáveis frequentemente usadas no Access Bank automaticamente.

A Memória de Programa: Flash de 32 KB

A memória de programa do PIC18F4550 tem capacidade de 32.768 bytes (32 KB), organizada em 16.384 palavras de 16 bits. O Program Counter tem 21 bits e aponta em incrementos de 2 (cada palavra de instrução ocupa 2 endereços de byte). O vetor de reset está no endereço 0x0000, e o vetor de interrupção de alta prioridade está em 0x0008.

Mapa da Memória de Programa

| Endereço | Conteúdo |

|---|---|

| 0x000000 | Vetor de Reset |

| 0x000008 | Vetor de Interrupção Alta Prioridade |

| 0x000018 | Vetor de Interrupção Baixa Prioridade |

| 0x000020 – 0x007FFF | Código do usuário (32.736 bytes úteis) |

| Acima de 0x007FFF | Não implementado |

O compilador XC8 cuida automaticamente de colocar o código de inicialização no vetor de reset. Você raramente precisará se preocupar com isso, mas saber que existe é importante para entender por que seu programa sempre começa a executar no mesmo lugar.

Acessar Flash como Dado: Tabelas de Constantes

A instrução TBLRD (Table Read) permite ler um byte da memória de programa como se fosse dado. Ela usa o registrador de 21 bits TBLPTR como ponteiro para a Flash e deposita o byte lido em TABLAT. O compilador XC8 gera esse acesso automaticamente quando você declara variáveis com qualificador const no escopo global.

Isso tem implicação direta no Projeto Integrador: tabelas como a de seno/cosseno para geração de sinais, mapas de caracteres para o display LCD ou tabelas de calibração de sensores devem ser declaradas como const para evitar consumir a preciosa RAM de 2 KB.

Aprofundando CISC versus RISC: Evidências Históricas

Há um aspecto do debate CISC versus RISC que frequentemente surpreende quem estuda o assunto pela primeira vez: o desempenho relativo das duas abordagens não é determinado apenas pelo número de instruções executadas por programa, mas pelo produto entre o número de instruções e o tempo por instrução.

O Argumento do CISC

Projetistas CISC defendiam que instruções mais poderosas reduziriam o número de instruções executadas por programa (N diminui), mesmo que cada instrução levasse mais ciclos para executar (CPI — Cycles Per Instruction — aumenta). O raciocínio era que o ganho em N compensaria o aumento em CPI.

Formalmente, o tempo de execução de um programa pode ser expresso como:

Equação Fundamental de Desempenho (revisão do Módulo 1)

T = N \times CPI \times T_{clock}

Onde:

- T é o tempo total de execução

- N é o número de instruções executadas

- CPI é a média de ciclos por instrução

- T_{clock} é o período do clock (inverso da frequência)

O CISC aposta em \downarrow N para compensar \uparrow CPI. O RISC aposta em \downarrow CPI e \downarrow T_{clock} (chip mais simples = clock mais alto).

A Descoberta que Mudou Tudo

Os pesquisadores de Berkeley e Stanford mediram empiricamente o que os programas reais faziam. O resultado foi surpreendente: em programas típicos escritos em linguagens de alto nível (C, Fortran, Pascal), as instruções mais comuns eram movimentos de dados, somas simples e desvios condicionais — as mesmas operações elementares que existiam nas primeiras ISAs dos anos 1950.

As instruções complexas do VAX e similares eram raramente executadas. Pior: para implementar hardware capaz de executar essas instruções, os projetistas precisavam de microcódigo extenso e circuitos complexos que, paradoxalmente, tornavam as instruções simples mais lentas também — porque o hardware estava cheio de lógica especializada para os casos raros.

A solução RISC era elegante em sua simplicidade: remover toda a complexidade desnecessária, construir hardware que executasse as instruções simples em 1 ciclo, e deixar que o compilador combinasse múltiplas instruções simples para realizar as operações que antes eram feitas por uma única instrução complexa. O compilador gera mais instruções (N aumenta), mas cada instrução é tão rápida (CPI próximo de 1 e clock mais alto) que o produto N \times CPI \times T_{clock} acaba menor.

O Caso Moderno: ARM como RISC Dominante

O ARM (Advanced RISC Machine) começou como projeto acadêmico na Acorn Computers em 1985, fortemente inspirado pelos projetos RISC de Berkeley. Sua ISA original tinha apenas 26 instruções! Hoje, a família ARMv8 tem centenas de instruções (incluindo extensões para SIMD, ponto flutuante e criptografia), mas ainda mantém o núcleo RISC de instruções de comprimento fixo de 32 bits (ou 16 bits no modo Thumb).

O resultado é que o ARM está em praticamente todos os smartphones, tablets, roteadores domésticos e dispositivos IoT do mundo. No momento em que você lê este material, há aproximadamente 250 bilhões de chips ARM em uso — a maioria das pessoas interage com processadores ARM dezenas de vezes por dia sem saber.

O que isso tem a ver com o PIC18F4550? O PIC é, em espírito, primo do ARM: ambos são arquiteturas RISC de comprimento de instrução relativamente fixo, projetadas para eficiência energética e simplicidade de implementação. A diferença fundamental é a escala: o ARM opera em 64 bits com bilhões de transistores, enquanto o PIC18 opera em 8 bits com alguns milhares de transistores. Mas os princípios arquitetônicos subjacentes são os mesmos que você está aprendendo.

Exercitando a Intuição: Estimando Custo de Código

Uma habilidade valiosa para quem programa sistemas embarcados é a capacidade de estimar, sem rodar o código, quanto tempo uma operação vai levar. Com o que você aprendeu sobre o conjunto de instruções do PIC18F4550 e seus tempos de execução, pode fazer isso.

O PIC18F4550 a 8 MHz tem um clock de instrução de 2 MHz (cada instrução usa 4 ciclos de clock). Isso significa que cada instrução de 1 ciclo leva 500 ns, e cada instrução de 2 ciclos leva 1 µs.

Exemplo: Estimando o Tempo de uma Multiplicação de 16 bits

O PIC18F4550 tem multiplicador de hardware de 8×8 bits (MULWF). Para multiplicar dois números de 16 bits (A × B), o resultado pode ter até 32 bits e precisa ser decomposto:

A_{16} \times B_{16} = (A_H \cdot 2^8 + A_L) \times (B_H \cdot 2^8 + B_L)

= A_H \cdot B_H \cdot 2^{16} + (A_H \cdot B_L + A_L \cdot B_H) \cdot 2^8 + A_L \cdot B_L

São necessárias 4 multiplicações de 8×8, cada uma em 1 ciclo (MULWF), mais cerca de 12–15 instruções de adição e movimentação para compor o resultado de 32 bits. Total: aproximadamente 16–20 ciclos = 8–10 µs a 8 MHz.

Compare com uma divisão de 16 bits por software, que pode exigir 100–200 ciclos no PIC18. Essa é a razão pela qual sistemas embarcados preferem evitar divisão e substituir por multiplicação ou deslocamento quando possível.

Pilha de Hardware: Chamadas Aninhadas e Seus Limites

Um aspecto da arquitetura que merece atenção especial é a pilha de hardware do PIC18F4550. Diferentemente dos processadores de uso geral que têm pilha na RAM (praticamente ilimitada), o PIC18 tem uma pilha de 31 níveis implementada em hardware dedicado.

Cada nível armazena um endereço de retorno de 21 bits (para os 32 KB de Flash). Quando você chama CALL, o endereço de retorno é empilhado; quando executa RETURN, é desempilhado. Se você tentar empilhar o 32º nível, o Stack Overflow ocorre — e o comportamento é indefinido (em versões mais modernas dos PIC, há detecção de overflow via flag).

Cuidado: Stack Overflow no PIC18F4550

/* PROBLEMA: Recursão no PIC18F4550 */

/* Esta função vai causar stack overflow! */

uint16_t fatorial(uint8_t n) {

if (n == 0) return 1;

return n * fatorial(n - 1); /* chamada recursiva — empilha PC */

}

/* fatorial(31) já transbordaria a pilha de 31 níveis! */

/* SOLUÇÃO: Use iteração, não recursão */

uint16_t fatorial_iterativo(uint8_t n) {

uint16_t resultado = 1;

while (n > 1) {

resultado *= n;

n--;

}

return resultado;

}A regra prática para o PIC18F4550: nunca use recursão em aplicações de microcontroladores. Além do limite da pilha, a recursão é inerentemente imprevisível em termos de consumo de memória em tempo de execução — algo inaceitável em sistemas embarcados confiáveis.

Resumo Visual: O Caminho de uma Instrução

Para encerrar este módulo, vamos traçar o caminho completo de uma instrução desde o momento em que é buscada da memória de programa até a conclusão da operação. Isso vai conectar o que você aprendeu aqui com o que estudará no Módulo 4 (Caminho de Dados da CPU).

sequenceDiagram

participant PC as Program Counter

participant Flash as Memória de Programa (Flash)

participant IR as Instruction Register

participant DEC as Decodificador

participant ALU as Unidade Lógica-Aritmética

participant RAM as Memória de Dados (RAM)

participant W as Registrador W

PC->>Flash: Apresenta endereço atual

Flash->>IR: Retorna instrução de 16 bits

PC->>PC: PC = PC + 2 (aponta para próxima instrução)

IR->>DEC: Envia bits da instrução para decodificação

DEC->>DEC: Identifica opcode, operandos, modo de endereçamento

DEC->>RAM: Lê operandos da memória (se necessário)

RAM->>ALU: Fornece operando f

W->>ALU: Fornece operando W (acumulador)

ALU->>ALU: Executa operação (ADD, AND, etc.)

ALU->>RAM: Escreve resultado (se destino = f)

ALU->>W: Escreve resultado (se destino = W)

ALU->>DEC: Atualiza flags (Z, C, N, OV) no STATUS

Esse diagrama simplificado mostra as fases fundamentais: busca (fetch), decodificação (decode), execução (execute) e escrita de resultado (write-back). No Módulo 4, você verá como esses componentes são interligados fisicamente no caminho de dados, e no Módulo 6 aprenderá como o pipeline paralelliza essas fases para aumentar o desempenho.

Conclusão do Módulo

Você chegou ao final de um módulo denso e fundamental. Vamos recapitular o que você aprendeu.

A ISA — Instruction Set Architecture — é a fronteira entre hardware e software. Ela define o contrato que permite que programas escritos hoje rodem em processadores de daqui a dez anos. Compreender a ISA é compreender o hardware pelo olhar do programador.

As instruções de máquina têm estrutura precisa: um opcode que identifica a operação e campos de operandos que especificam onde os dados estão. O modo de endereçamento determina como o endereço efetivo do operando é calculado — e a escolha do modo correto afeta diretamente o desempenho e o tamanho do código.

As filosofias RISC e CISC representam dois pontos em um espectro de compromissos de projeto. O RISC — da qual o PIC18F4550 é um representante — prioriza instruções simples e uniformes que executam rapidamente e se prestam bem ao pipeline. O CISC prioriza instruções poderosas que fazem mais por instrução, a custo de maior complexidade de decodificação. Os processadores modernos, como o x86, encontraram uma terceira via: manter compatibilidade com a ISA CISC historicamente acumulada, mas implementar internamente um núcleo RISC de alto desempenho.

O PIC18F4550, com suas 75 instruções organizadas em cinco categorias, é um estudo de caso concreto e acessível de todos esses princípios. Você agora tem as ferramentas para ler o assembly gerado pelo compilador, entender por que certas construções em C são mais caras do que outras, e até mesmo escrever trechos críticos diretamente em assembly quando justificado.

No próximo módulo, você vai abrir a CPU por dentro: vai explorar o caminho de dados — a ULA, o banco de registradores, os barramentos internos — e entender como esses componentes trabalham juntos para executar cada uma das instruções que você estudou aqui.

Antes da próxima aula: Certifique-se de ter o MPLAB X instalado e funcionando com o compilador XC8. Explore a janela de Disassembly Listing com algum código do Módulo 2 já compilado. Tente identificar pelo menos três modos de endereçamento diferentes no assembly gerado. Traga suas observações para a sessão de tutoria!